Not a huge surprise, but in data-intensive applications, the new system can provide a significant advantage.

AMD is still at Computex last year Presented A cache called 3D V-Cache, which is essentially a chip that provides 64MB of additional L3 capacity built on top of the existing Zen 3 chip. However, the company did not go into deep technological detail, but this was also replaced during this year’s ISSCC, and Hardwarelux I also provided this information.

(source: Hardwarelux) [+]

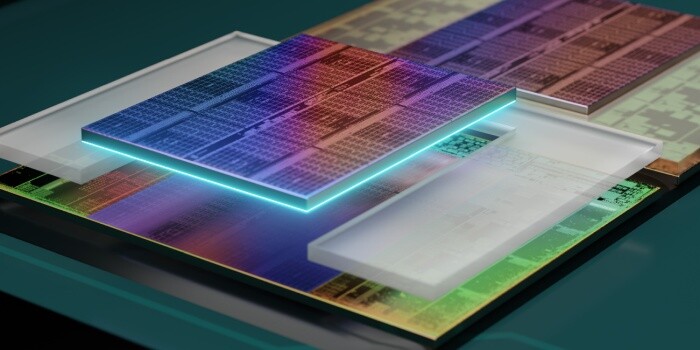

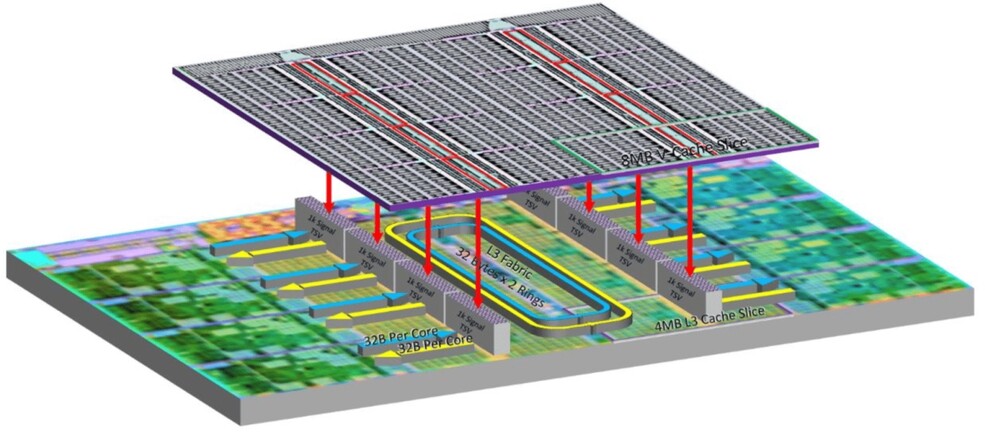

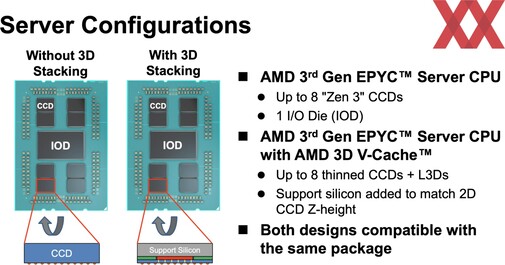

AMD introduced the system based on the design of EPYC 7003 processors, and the important factor was that the additional chip required turning over CPU chips containing Zen 3 cores. These became significantly thinner, so the 3D cache could fit vertically, as well as That the residual height difference compared to the original foil was filled with negative silicon. As a result, CPU chips are very high on EPYC processors without and without 3D V-Cache, and this goes along with the IO chip, making encapsulation easier. AMD used TSMC’s SoIC technology to encapsulate and layer the chips on top of each other.

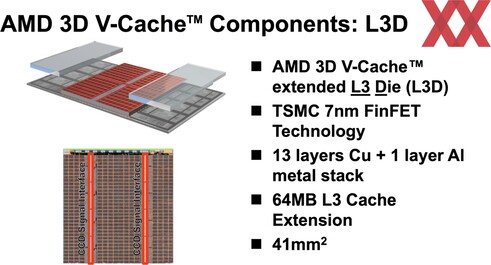

The chip that provides the 3D cache itself has a size of 41mm² and is made on a 7nm node from TSMC. The 64MB SRAM is divided into eight 8MB chips, each connected to the 4MB L3 cache on the Zen 3 chiplet via a 1024-pin TSV interface. The communication power is more than 2 Tbps per chip, which adapts to the ring bus rate used to connect the chips on the chip. With this said, basically every core doesn’t matter whether the data is in one of the L3 of the Zen 3 chip or the chip linked from the 3D cache on top of it.

One of the biggest difficulties with such designs is latency, as the 3D cache is physically located on top of the chip. To reduce these shortcomings, AMD built 3D V-Cache in the same way as the L3 cache, which means that the data macros remain 128KB, but instead of 256, there are actually 512 on the additional chip. Obviously, the latter is due to increased capacity. In addition, 3D V-Cache uses 1088 6KB member macros to help you find data quickly. With this deployment, AMD says it only takes an additional four cycles to delay the Zen 3’s L3 cache, which is hugely worth it, considering the ability to triple the L3 cache’s capacity.

Finally, it is worth avoiding consumption. Although stashes are not the most appetizing ingredient, they clearly do not function without energy. To reduce power consumption to a minimum, AMD has implemented a number of improvements, but the effect of 3D V-Cache will still be felt. If it is not possible to increase the TDP frame, the change can be compensated for by reducing the CPU core clock. This can be seen, for example, on the Ryzen 7 5800X3D, which pushes 300MHz for an extra 64MB of cache compared to the Ryzen 7 5800X while still keeping its 105W TDP frame. However, in data-intensive applications, the advantage of doubling the capacity of the L3 cache is so powerful that it significantly compensates for the recovered clock.